# **Comparison of Various Multi-core Processor using FPGA**

<sup>1</sup>N.Dhasarathan

<sup>1</sup>Professor, Department of ECE, BVC Engineering College, Andhra Pradesh, India.

<sup>1</sup>dhasarathan.raja@gmail.com

Abstract: The Embedded multiprocessor center is a structure reasoning that has become a standard in Scientific and designing applications. The FPGA license complex rationale frameworks executed on single programmable gadgets. The Embedded multiprocessors face another issue with string wellbeing. The structured processor design comprises of on-chip transmitter and collector modules alongside the handling and controlling units to empower the information transmission and gathering on a solitary pass on. The information move is practiced with less number of directions as contrasted and the broadly useful processor. The interface encourages the plan of coprocessors that require complex control to deal with information subordinate I/O, sparing/reestablishing task state upon task switches, and pipelined handling. This paper presents how this interface empowers the plan of such reusable yet savvy coprocessors.

Key words: Embedded system design, SoC, ASIP, Data transfer.

## Introduction:

The coming of new media applications, for example, time-move recording, 3D games, video conferencing, and MPEG-4-like intuitiveness requests an expanding adaptability of buyer gadgets items. Besides, the variety in the necessary arrangement of uses per item, per nation, and after some time as measures advance requires a vital methodology. Overseeing multifaceted nature, plan cost, and time-to-market of such asset compelled machines requires a nonexclusive and adaptable media-handling stage that can be sent in a wide scope of items. Presently, a few sellers are entering the market with stages that address these issues somewhat [1],[2]. In addition, the coprocessors are performing various tasks and can time-share assignments from a lot of uses. Along these lines, application multifaceted nature isn't limited to the quantity of coprocessors in the engineering. For example, a delegate medium-grain work is the discrete cosine change (DCT) required for MPEG encoding and translating.

**Corresponding Author:** N.Dhasarathan, Professor Department of ECE, BVC Engineering College Andhra Pradesh, India, Mail: <u>dhasarathan.raja@gmail.com</u>

Volume No.1, Issue No.1 (2020)

# Journal of Science Technology and Research (JSTAR)

An Eclipse DCT coprocessor may time-share the converse and forward DCT capacities required for simultaneous MPEG-2 encoding and disentangling in a period move recording application. The ASIPs have discovered broad use in some certifiable applications in view of their effective guidance set and equipment. Especially in the installed frameworks like movement or vibration finders, temperature and mugginess pointers should be run more often than not on the batteries. So the force utilization of the framework assumes a basic job in the activity of the framework. Rather than utilizing a microcontroller or the microchip in such applications the ASIPs can perform better. To move information from a remote area, the ordinary inserted frameworks need to utilize microcontroller or microchip and some application explicit equipment. In addition here and there the microcontrollers will have pointless equipment (in regards to the application) that is incorporated onto them [5].

Multiprocessors are important to have the option to speak with one another. Normally by means of a common memory, where esteems that different processors can utilize and put away. This presents the new issue of string safety [6]. At the point when string security is abused, two processors get to a similar incentive simultaneously. For this every processor to have some neighborhood memory, where the processor doesn't need to consider string wellbeing to accelerate the processor. So that the every processor needs to have a nearby memory.

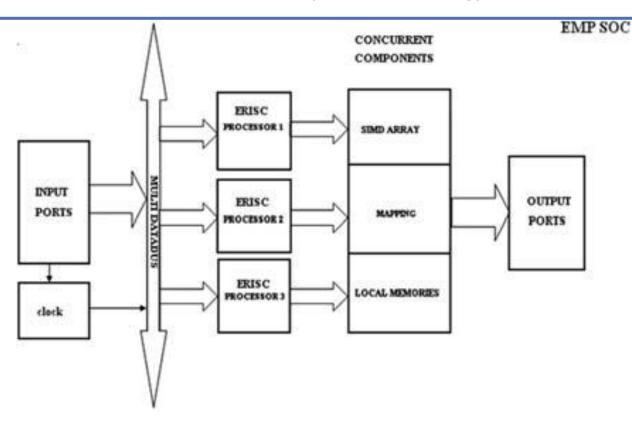

#### **Proposed Multi-Core Architecture**

This multiprocessor center design is completely designed in the wake of actualizing towards the inserted simultaneous processor. The simultaneous parts like SIMD exhibit, planning and nearby recollections are added to every processor as appeared in Fig.2. These modules autonomously fill in as an embedded multi-processor center that includes the both equal and circulated simultaneous strategy [3]. The planned multiprocessor center executes the different errands by utilizing simultaneous figuring techniques [8].

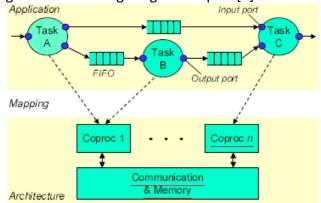

Fig.1. Architecture mapping and its applications

Figure 1 delineates how application errands are planned onto the coprocessors. Overshadowing applications are determined as a lot of errands that speak with one another through FIFO channels [4]. A channel interfaces with the yield port of a delivering task and the information port of at least one expending errands. Application channels are planned onto information streams with cushions designated in shared on-chip memory.

# Journal of Science Technology and Research (JSTAR)

#### Fig.2. A Novel E.C.C Architecture

# I/o ports

Every processor having the three ports and each port independently eight I/o lines. Absolutely 24 I/O lines for every processor. It gathers the information and send to the handling unit. At the point when it is prepared after outcomes are sent back to yield ports.

# Journal of Science Technology and Research (JSTAR)

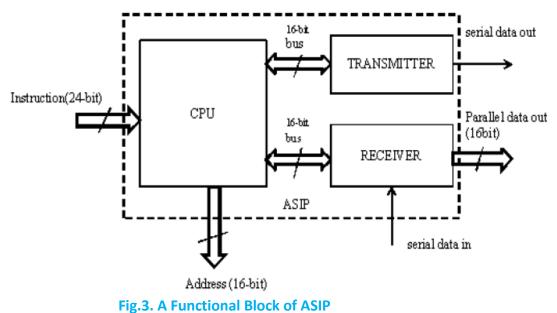

Fig. 3 shows the square graph of the ASIP being portrayed. The framework comprises of a 16-piece handling unit and transmitter and collector areas which are interfaced to the CPU to help the information move. The focal handling unit of the ASIP comprises of 16-piece address and information transports [7]. The ALU (Arithmetic Logical Unit) is a fixed point number sort which performs 16-piece math and coherent procedure on the sensor information. The coherent tasks are utilized for testing of the sensor information and the number juggling activities are utilized to control the information. The CPU[8] likewise comprises of 8 universally useful registers (R0-R7) every one of 16 bits wide. There are no specific reason registers in the CPU like gatherer and there is no need among them.

## Pipelining

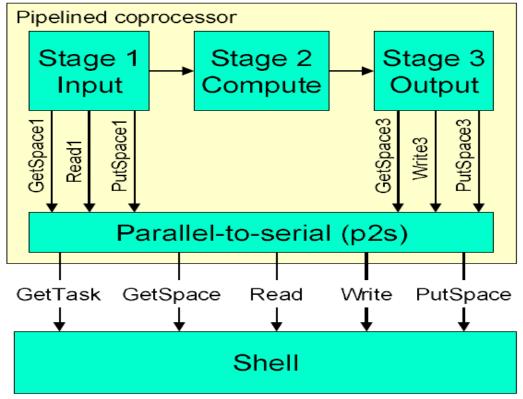

Contingent upon application prerequisites, the coprocessor may should be pipelined. For instance, assume the capacity gave by the coprocessor is a 2-dimensional DCT varying for MPEG video pressure and decompression, requiring a solitary inputstream and a solitary yield stream. Assume further that perusing an input parcel takes around 30 clock cycles, and furthermore composing a yield bundle takes 30 cycles, while just 50 patterns of complete figure time are accessible (for example for concurrent interpreting of two HD MPEG-2 streams at 150 MHz). In such cases, it is beneficial thinking about whether the coprocessor can be structured in a pipelined design, to such an extent that the info stage can work simultaneously to the process and yield stages. For whatever length of time that the stages are not obliged by accessible correspondence data transmission to the shell, this gives a reasonable choice.

Fig.4. A model Pipelined Co-Processor

# **Results and Discussions**

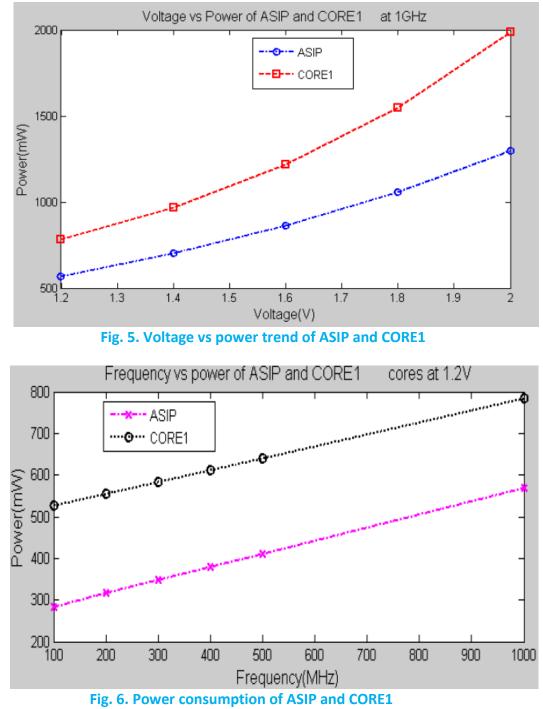

The figures 5 and 6 gives similar perspective on the force utilization of the ASIP and CORE1. In the figure 5, the deviation of the bends shows that as the working voltage is expanding the force utilization of the CORE1 builds all the more quickly when contrasted and ASIP power.

Volume No.1, Issue No.1 (2020)

The variety of intensity regarding recurrence for the ASIP and CORE1 is appeared in figure 6.Different FPGA implementation results for the proposed system are shown in Figures 5 and 6. It shows that there is a significant improvement in Speed and occupies optimum Area using 90nm technology Xilinx FPGA's, when compared to existed system [9]. CONCLUSION

The multiprocessor core has been designed and verified through exhaustive simulations. It is observed that the overall delay of the multiprocessor core is 4.674ns. The overall Area is 10,505 and speed is 213.949MHz. The ASIP designed for the data transfer integrates a processing unit and individual transmitter and receiver onto the single chip. The results shows that the ASIP design occupies less space and consumes less power. The interface as defined in this paper separates computation (coprocessors) from generic infrastructure aspects to facilitate reuse of coprocessors over different architecture instances. The generic infrastructure offers multi-tasking, synchronization, and data transport services to the coprocessors in the form of five interface primitives. These interface primitives relieve the coprocessor designer from addressing cumbersome system-level issues.

## Reference:

1. S. Dutta, R. Jensen, and A. Rieckmann, .Viper: A Multiprocessor SOC for Advanced Set-Top Box and Digital TV Systems., IEEE Design and Test of Computers, pp. 21-31,Sept-Oct. 2001.

2. W. Lee and C. Basoglu, .MPEG-2 Decoder Implementation on MAP-CA Media processor using the C Language., Proc. of the SPIE: Media Processors 2000, 3970, Jan. 2000.

3.Sathiyanathan, N., 2018. Medical Image Compression Using View Compensated Wavelet Transform. Journal of Global Research in Computer Science, 9(9), pp.01-04.

4. S. Vercauteren, B. Lin, and H. de Man, .Constructing Application-Specific Heterogeneous Embedded Architectures for Custom HW/SW Applications., 33rd Design Automation Conf. (DAC), pp. 521-526, June 1996, Las Vegas, Nevada,

# USA.

5. Mohan.R, Land.I, "Building Integrated ARINC 429 Interfaces using an FPGA". Actel Corporation, Mountain View, California, 2005.

6. Karthick, R., 2019. Design of Low Power MPSoC Architecture using DR Method. Asian Journal of Applied Science and Technology (AJAST), 3(2), pp.101-104.

7. Rose.J, GamaL.A.E, and A. Sangiovanni Vincentelli.A, "Architecture of Field-Programmable Gate Arrays," Proc. IEEE, vol. 81, no. 7, July 1993, pp.1013-102.

8. Kamaraju, M., Lalkishore, K., Tilak, A.V.N. : A novel implementation of Application Specific Instruction-set Processor (ASIP) using Verilog. Journal of World Academy of Science, Engineering and Technology (WASET), Paris, Issue 59, pp. 382-387, November (2011).

9. Karthick, R. and Sundararajan, M., 2017. PSO based out-of-order (ooo) execution scheme for HT-MPSOC. Journal of Advanced Research in Dynamical and Control Systems, 9, p.1969.