Author:

Parimala Gandhi Ayyavu, Jemima SPublished in

Journal of Science Technology and Research( Volume , Issue )

ABSTRACT:

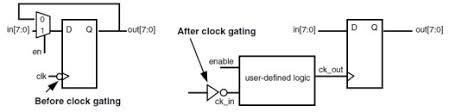

Modern semiconductor circuits frequently encounter timing errors due to high clock frequencies and reduced supply voltages. Even minimal disturbances can threaten timing margins. While various correction techniques exist, most introduce delays and complexity, resulting in hardware overhead and timing problems. In our proposed method, we implement a novel timing-error-tolerant system that instantly corrects errors by modifying the flip-flop clock mechanism. This solution eliminates clock-cycle loss while maintaining system timing. To further reduce power consumption during inactive stages, we incorporate Look-Ahead Clock Gating (LACG), which computes enabling signals one cycle ahead using XOR outputs from flip-flops. LACG avoids tight timing constraints and supports larger, general designs by allotting a full clock cycle for signal propagation. We latch the XOR output using an enhanced AGFF to preserve its validity during the entire positive half-cycle. Due to its simplicity and efficiency, our system achieves instant timing-error recovery with minimal hardware overhead.

INTRODUCTION:

As clock frequencies rise and supply voltages drop, timing errors become increasingly frequent in digital circuits. These errors primarily affect critical paths, especially under variations in CMOS process, voltage, and temperature (PVT) conditions. At 0.4 V, for instance, the slowest logic paths can become 12 times slower than under typical conditions. Additionally, transistor aging effects—particularly negative-bias temperature instability (NBTI)—further aggravate timing errors by increasing path delays. Such challenges demand robust timing-error-tolerant methods for reliable system design. We address these issues by introducing a timing recovery method that modifies flip-flop clocks to correct errors instantly. This method prevents performance loss without disrupting clock-based operations. Additionally, we employ Look-Ahead Clock Gating (LACG) to reduce power consumption, especially in inactive logic stages. LACG generates clock gating signals in advance, avoiding timing bottlenecks and supporting broad-scale circuit designs. These combined strategies enhance timing reliability and power efficiency in advanced semiconductor systems.